At previous week’s Intel Architecture Day, Intel’s main architect, Raja Koduri, briefly held up the smallest member of the company’s forthcoming Xe-HP collection of server CPUs, the 1 tile configuration. Now, only a several days later on, he has upped the ante by demonstrating off the largest, four tile configuration.

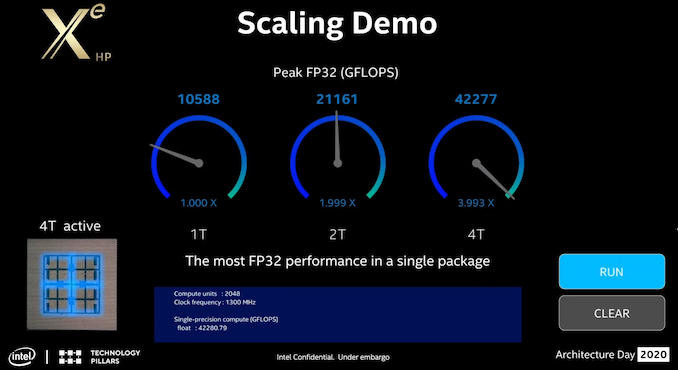

Intended to be a scalable chip architecture, Xe-HP is established to be obtainable with one, two, or four tiles. And even though Intel has yet to disclose also a lot in the way of particulars on the architecture, based on their packaging disclosures it seems like the enterprise is making use of their EMIB tech to wire up the GPU tiles, as perfectly as the GPU’s on-bundle HBM memory.

Assuming it would make it to market, a multi-tiled GPU – basically numerous GPUs in a single package – would be a significant accomplishment for Intel. GPUs are notoriously bandwidth-hungry due to the want to shovel facts all around involving cores, caches, and command frontends, which helps make them non-trivial to break up up in a chiplet/tiled manner. Even if Intel can only use this type of multi-tile scalability for compute workloads, that would have a considerable affect on what kind of general performance a single GPU offer can achieve, and how long run servers may possibly be designed.

Freelance twitter maven. Infuriatingly humble coffee aficionado. Amateur gamer. Typical beer fan. Avid music scholar. Alcohol nerd.